Entities | |

| mos_6502_datapath.rtl | architecture |

Ports | ||

| data | inout | std_ulogic_vector ( 7 downto 0 ) |

| The external-facing data pins. | ||

| address | inout | std_ulogic_vector ( 15 downto 0 ) |

| The external-facing address pins. | ||

| phi1 | in | std_ulogic |

| Ricoh_2A03_PHI1 | ||

| phi2 | in | std_ulogic |

| Ricoh_2A03_PHI2 | ||

| databus_SB | inout | std_ulogic_vector ( 7 downto 0 ) |

| The SB bus | ||

| databus_DB | out | std_ulogic_vector ( 7 downto 0 ) |

| The DB bus | ||

| databus_ADH | out | std_ulogic_vector ( 7 downto 0 ) |

| The ADH bus | ||

| databus_ADL | out | std_ulogic_vector ( 7 downto 0 ) |

| The ADL bus | ||

| load_SB_AC | in | std_ulogic |

SB/AC - Load from SB bus into the accumulator | ||

| output_enable_AC_SB | in | std_ulogic |

AC/SB - Enable Accumulator output to SB bus | ||

| output_enable_AC_DB | in | std_ulogic |

AC/DB - Enable Accumulator output to DB bus | ||

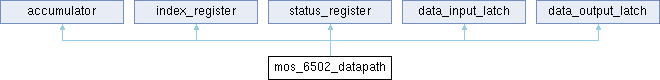

Wrapper component holding the data input/output latches, the index registers, the address registers, and the status register. TODO: Add precharge and drain MOSFETs

|

Port |

The external-facing address pins.

|

Port |

The external-facing data pins.

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

Ricoh_2A03_PHI1

|

Port |

Ricoh_2A03_PHI2