Entities | |

| logic_core.rtl | architecture |

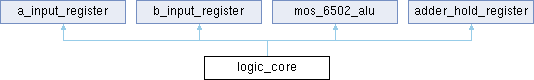

The Arithmetic Logic Unit of the 6502, plus the B and A input registers.

This file combines all the cores of the ALU into one subunit that can be dropped in to a 6502 core. The internal signal routing is handled by this core to minimize the possibility of signal wiring mistakes in higher level designs, and ideally will be optimized out at synthesis time as there's no real logic in this core itself. All actual logic is implemented in the components that this core references.

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

|

Port |

Ricoh2A03_2A03_Phi2

|

Port |

|

Port |

|

Port |

|

Port |